Hoch statt flach: Nanodrähte für eine neue Chip-Architektur

Silizium ist das gängige Material in der Elektronik, egal, ob es um Handys, Solarzellen oder Computer geht. Drähte aus Silizium im Nanometer-Bereich haben ein großes Potential für eine völlig neue Chip-Architektur, doch muss man zuvor ihre elektrischen Eigenschaften noch genauer erforschen und verstehen. Forscher vom Max-Planck-Institut für Mikrostrukturphysik und vom Forschungszentrum Dresden-Rossendorf (FZD) gelang es, den elektrischen Widerstand und den bislang unbekannten Stromfluss im Inneren von Silizium-Nanodrähten darzustellen.

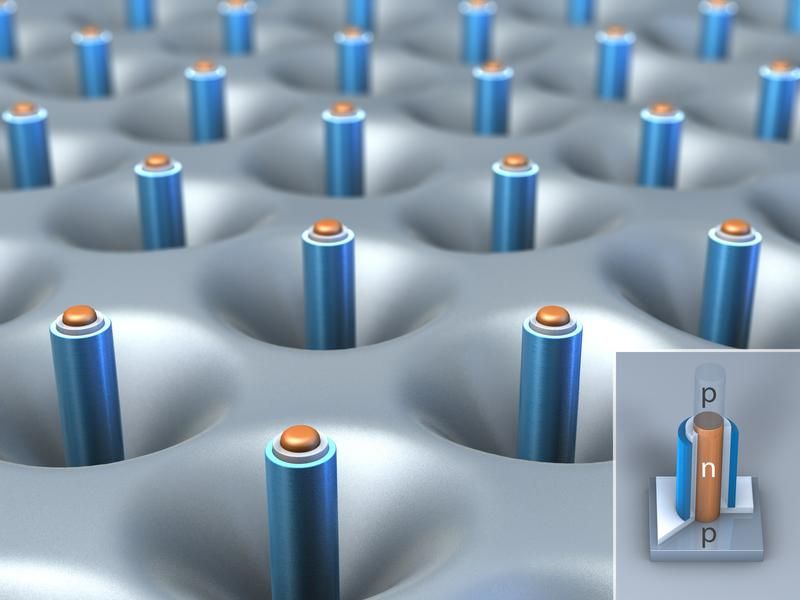

Schema eines Silizium-Wafers mit neuartigen Säulen-Transistoren aus Silizium-Nanodrähten (ohne oberen p-Kontakt).

Sander Münster, Kunstkosmos Dresden

Unzählige Silizium-Transistoren sind auf einem heutigen Mikrochip dafür verantwortlich, Informationen weiterzugeben. Die Transistoren sind in der Ebene, also flach, angeordnet und mittlerweile nur noch rund 50 Nanometer groß. Da einer weiteren Miniaturisierung Grenzen gesetzt sind, wird fieberhaft an neuen Ansätzen gearbeitet. Man stelle sich nun eine ganz neuartige, dreidimensionale Architektur vor: statt flächig oder in Schichten übereinander gestapelt, werden die Silizium-Transistoren einfach um 90 Grad gedreht und in die Höhe gebaut. So könnte man viele Transistoren, die wie winzige Säulen mit Durchmessern von jeweils nur wenigen Nanometer aus dem Mikrochip herausragen, auf der Fläche eines üblichen, flächigen Transistors unterbringen. Damit wäre der Schritt von der Mikro- zur Nanoelektronik endgültig getan.

Nanodrähte aus Kohlenstoff haben mittlerweile in der industriellen Fertigung Einzug gehalten, Drähte aus Silizium hingegen können erst seit kurzem zuverlässig hergestellt werden. Vor ihrem Einsatz müssen sie jedoch noch erforscht werden, denn nur wenn man ihre elektrischen Eigenschaften sehr gut versteht, kann man zuverlässige Transistoren für eine neue Generation von Mikrochips bauen. In solchen Säulen-Transistoren wird der Strom nicht horizontal, sondern vertikal fließen, und sie werden kleiner und energiesparender sein als heute üblich. Nicht zuletzt verspricht man sich von Silizium-Nanodrähten auch hocheffiziente Solarzellen.

Die Max-Planck-Forscher aus Halle stellen einkristalline Nanodrähte aus Silizium her, die besonders gut geeignet sind als Bauteile für Mikrochips. Im Ionenstrahlzentrum des FZD werden in die Drähte Fremdatome implantiert, ein Vorgang, der den Stromfluss im Halbleiter-Material überhaupt erst ermöglicht - und damit auch den Transistor, dessen Funktion es ist, den Strom der elektrischen Ladungsträger zu schalten. Silizium selbst ist zwar hervorragend erforscht, doch gilt dies nicht, wenn man sich auf die Nanometer-Ebene begibt. "Wir haben zunächst Drähte untersucht, die einen Durchmesser von rund 100 Nanometer haben und 300 Nanometer lang sind. Das Ziel richtet sich jedoch auf Drähte, die nur wenige Atome dick sind bis hin zu einem Draht, wo sich nur noch einzelne Atome aneinander reihen. Deren Materialverhalten wollen wir dann genau charakterisieren um herauszufinden, wie man ihre elektrischen Eigenschaften für den Einsatz in der Nanoelektronik maßschneidern kann, z.B. für neuartige Feldeffekt-Transistoren.", so der FZD-Physiker Dr. Reinhard Kögler.

Was die Wissenschaftler bisher gefunden haben: die implantierten Fremdatome - es handelt sich um für die Mikroelektronik typische Sorten wie Bor oder Phosphor - bleiben nicht an Ort und Stelle, sondern wandern zum Rand des Nanodrahtes, also zur Oberfläche hin. Dort werden sie teilweise inaktiv und können dann nicht mehr zur Leitfähigkeit beitragen. Bisher jedoch fehlte eine geeignete Messmethode, um die Auswirkungen der ungleichen Verteilung der implantierten Atome zu bestimmen. Sollen also zukünftig Nanodrähte als Säulen-Transistoren zum Einsatz kommen, so müssen die Entwickler diese - und weitere - Erkenntnisse sorgfältig berücksichtigen.

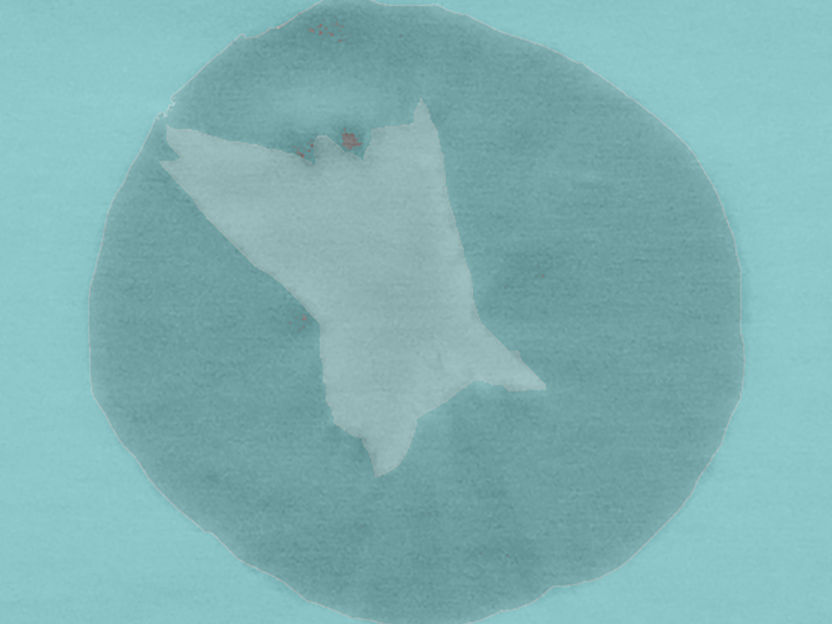

Die Nanodrähte wurden in Rossendorf mit einer speziell hierfür abgewandelten Untersuchungsmethode (Scanning Spreading Resistance Microscopy, SSRM) untersucht. Diese Methode erlaubt es zugleich, während der Messungen die Nanodrähte der Länge nach Schicht für Schicht abzutragen und so quasi dreidimensionale Messungen durchzuführen. So erhalten die Wissenschaftler 3D-Bilder von der Leitfähigkeit in einem Nanodraht, der am Ende nur so dick ist wie der 25.000ste Teil eines menschlichen Haares.

Originalveröffentlichung: Xin Ou et al.; "Carrier Profiling of Individual Si Nanowires by Scanning Spreading Resistance Microscopy"; Nano Letters 2010,10,171-175

Meistgelesene News

Themen

Organisationen

Weitere News aus dem Ressort Wissenschaft

Holen Sie sich die Chemie-Branche in Ihren Posteingang

Mit dem Absenden des Formulars willigen Sie ein, dass Ihnen die LUMITOS AG den oder die oben ausgewählten Newsletter per E-Mail zusendet. Ihre Daten werden nicht an Dritte weitergegeben. Die Speicherung und Verarbeitung Ihrer Daten durch die LUMITOS AG erfolgt auf Basis unserer Datenschutzerklärung. LUMITOS darf Sie zum Zwecke der Werbung oder der Markt- und Meinungsforschung per E-Mail kontaktieren. Ihre Einwilligung können Sie jederzeit ohne Angabe von Gründen gegenüber der LUMITOS AG, Ernst-Augustin-Str. 2, 12489 Berlin oder per E-Mail unter widerruf@lumitos.com mit Wirkung für die Zukunft widerrufen. Zudem ist in jeder E-Mail ein Link zur Abbestellung des entsprechenden Newsletters enthalten.

Meistgelesene News

Weitere News von unseren anderen Portalen

Zuletzt betrachtete Inhalte

Schnellen Phasenumwandlungen auf der Spur - Einzigartige Kombination von experimentellen Techniken offenbart die Phasenumwandlung eines metallischen Glases